信號及電源完整性

測試印刷電路板上的高速數位線路

穩定,清晰的電源線信號是確保電子設計的良好性能的基礎。針對電源完整性測試,羅德與施瓦茨提供廣泛的工作台及手持式測試解決方案。傳輸信號通常會因串擾,帶寬限制以及阻抗不連續而能量衰減。羅德與施瓦茨廣泛的測量解決方案,可用於測試定時,抖動,回波及插入損耗,眼圖,串擾及干擾信號分量。

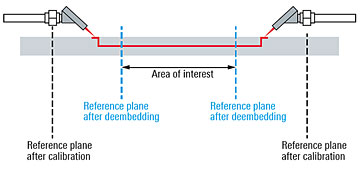

在執行多個任務(比如驗證PCB上的數字高速信號結構)的情況下,測量必須在某些層級上進行,不考慮探頭,探頭墊,通孔,引入線以及引出線的影響。這就需要使用準確的去嵌入算法來計算此類影響並將其從測量值中移除,只保留感興趣區域的結果。

R&S®ZNB20裝置可用於驗證最高20 GHz的PCB上的高速差分信號線路。

隨著數據傳輸速率的不斷提高,使得高速數字設計及組件的信號完整性變得更具挑戰性。尤其在其更高的數據率下,矢量網絡分析儀(VNA)逐漸取代傳統的時域反射計 TDR)裝置,可用於測試連接器,電纜,PCB等無源組件.VNA有助於提高準確性,速度以及ESD可靠性,是這個領域的理想之選。

測試解决方案

下述裝置例舉了驗證最高20 GHz的PCB上的高速差分信號線路。該測試裝置基於R&S®ZNB20四端口VNA。相應的去嵌入工具可直接在R&S®ZNB20上運行,比如Delta-L,EMStar Delta-L +,EMStar Smart Fixture Deembedding(SFD)或AtaiTec In-Situ Deembedding(ISD),消除了使用外部PC的必要性。除了要測量的實際信號跡線之外,PCB試樣通常還要包含一條更短的信號跡線,以促進此類去嵌入操作。差分PCB探頭(比如,來自PacketMicro的探頭)可用於將R&S®ZNB20連接到這些信號跡線。

流程自動化

測試通常是通過軟件自動化進行的,有效地簡化此流程並指導操作員完成整個測試步驟左側截圖例舉了該測試流程的三個步驟:

- 測量去嵌入的雙通(短)結構,結果位於左列

- 測量整體(長)結構,結果位於中列

- 基於選擇的去嵌入方法計算感興趣區域,結果位於右列

對於雙通(短)以及整體(長)測量,兩個探頭的阻抗以及時間將顯示在插入損耗上方。這樣方便快速判斷是否需要重新調節探頭。

眼圖

如需進一步調查,可使用R&S®ZNB-K20選件分析感興趣區域的眼圖。使用該選件,您可以驗證眼圖中加強,噪聲,抖動以及均衡的影響。此外,該選件亦可通過掩碼測試提供通過/失敗檢測及統計結果。

眼圖及測量值在頻域和時域中同時顯示

結論

R&S®ZNB提供了所有必要的功能,可一體化測試PCB上的數字高速信號結構。該儀器上亦可安裝其他的嵌入工具,以便消除探頭,探頭墊,通孔,引入線以及引出線的影響。